**DC-DC Converters**

# **DDR12 SERIES**

[ 2 YEAR WARRANTY ]

High current dual-output power module for DDR memory

Single compact module provides 25 A @ 2.5 V for V<sub>ddq</sub> supply and 8 A @ 1.25 V for V<sub>tt</sub> termination

- Tracking dual output voltages (1.25 V @ 8 A, 2.5 V @ 25 A)

- Output voltage remote sense

Sink capability for logic terminations

Power good output signal

**Overvoltage protection**

Dual output

**Overcurrent protection**

**Remote ON/OFF**

Available RoHS compliant

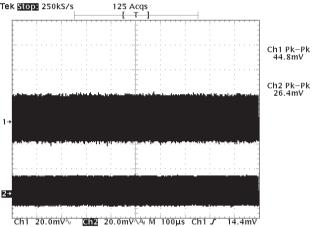

The dual output DDR12-25D08-AJ is specifically designed to meet the power needs of double data rate memory DIMMS and associated memory control logic. The  $V_{tt}$  output tracks the  $V_{ddq}$  output, while the  $V_{tt}$  output can sink current as required by logic terminations.This converter offers typical efficiencies greater than 84% when operated at 50% load or greater. This model features a wide input range as well as trimmable output voltages. Remote sense on V<sub>ddq</sub> and remote ON/OFF facilities are included as standard, and the converter is protected against overcurrent and over-voltage conditions.

**DC-DC Converters**

Stresses in excess of the maximum ratings can cause permanent damage to the device. Operation of the device is not implied at these or any other conditions in excess of those given in the specification. Exposure to absolute maximum ratings can adversely affect device reliability.

#### Absolute Maximum Ratings

| Characteristic             | Symbol                                          | Min  | Тур | Max     | Units  | Notes and Conditions                    |

|----------------------------|-------------------------------------------------|------|-----|---------|--------|-----------------------------------------|

| Input voltage - continuous | V <sub>in</sub> (cont)                          | -0.3 |     | 13.2    | Vdc    | V <sub>in(+)</sub> - V <sub>in(-)</sub> |

| Input voltage - nominal    | V <sub>in</sub> (nom)                           |      | 12  |         |        |                                         |

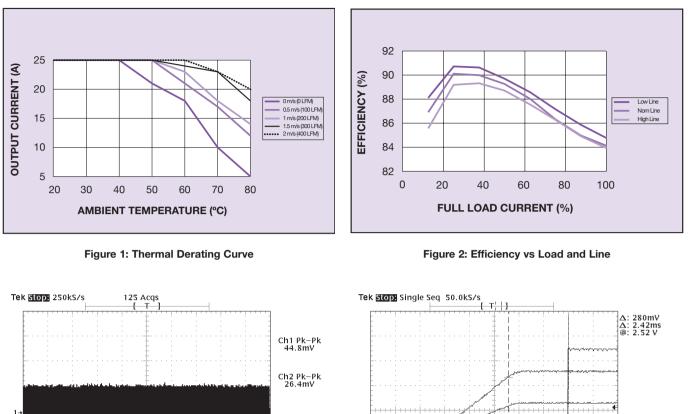

| Operating temperature      | Т <sub>ор</sub>                                 | 0    |     | 80      | °C     | Refer to derating guidelines and Note 1 |

| Storage temperature        | T <sub>storage</sub>                            | -40  |     | 125     | °C     |                                         |

| Output current             | I <sub>ddq</sub> (max)<br>I <sub>tt</sub> (max) |      |     | 25<br>8 | A<br>A |                                         |

All specifications are typical at V<sub>in</sub>(nom), V<sub>ddq</sub> = 2.5 V, V<sub>tt</sub> = 1.25 V and full load. Tests were performed at 25 °C unless otherwise stated.

#### Input Characteristics Characteristic Symbol Min Мах Units **Notes and Conditions** Тур V<sub>in</sub> (oper) 12 13.2 Input voltage - operating 10.8 Vdc Input current - min. load 400 mAdc V<sub>in</sub> (min) - V<sub>in</sub> (max), enabled lin I<sub>in</sub> (off) 20 Converter disabled Input current - Quiescent mAdc

#### Turn On/Off

| Characteristic             | Symbol                | Min | Тур  | Max  | Units | Notes and Conditions                                          |

|----------------------------|-----------------------|-----|------|------|-------|---------------------------------------------------------------|

| Input voltage - turn on    | V <sub>in</sub> (on)  | 10  | 10.2 | 10.4 | Vdc   |                                                               |

| Input voltage - turn off   | V <sub>in</sub> (off) | 9.7 | 9.9  | 10.1 | Vdc   |                                                               |

| Turn on delay - enabled,   | T <sub>delay</sub>    |     | 5    |      | ms    | With the enable signal asserted,                              |

| then power applied         | (power)               |     |      |      |       | this is the time from when the                                |

|                            |                       |     |      |      |       | input voltage reaches the                                     |

|                            |                       |     |      |      |       | minimum specified operating                                   |

|                            |                       |     |      |      |       | voltage until the POWER GOOD                                  |

|                            |                       |     |      |      |       | is asserted high                                              |

| Turn on delay - power      | T <sub>delay</sub>    |     | 5    |      | ms    | $V_{in} = V_{in}$ (nom), then enabled.                        |

| applied, then enabled      | (enable)              |     |      |      |       | This is the time taken until the                              |

|                            |                       |     |      |      |       | POWER GOOD is asserted                                        |

|                            | _                     |     |      |      |       | high                                                          |

| Output to POWER GOOD delay | T <sub>delay</sub>    |     | 3    |      | ms    | Output voltage in full regulation to POWER GOOD asserted high |

| Rise time                  | T <sub>rise</sub>     |     | 2    |      | ms    |                                                               |

**DC-DC** Converters

| Characteristic - Signal Name                                               | Symbol                | Min | Тур | Max  | Units | Notes and Conditions                                                               |

|----------------------------------------------------------------------------|-----------------------|-----|-----|------|-------|------------------------------------------------------------------------------------|

| At remote/control ON/OFF pin<br>Open collector or equivalent<br>compatible |                       |     |     |      |       | See Notes 2 and 3<br>See Application Note 133 for<br>Remote ON/OFF details         |

| High level input voltage                                                   | v <sub>ih</sub>       | 2.0 |     |      | V     | Converter guaranteed on wher<br>OUTEN pin is greater than V <sub>ih</sub><br>(max) |

| Low level input voltage                                                    | v <sub>il</sub>       |     |     | 0.80 | V     | Converter guaranteed off<br>when OUTEN pin is<br>less than V <sub>il</sub> (max)   |

| Low level input current                                                    | I <sub>il</sub> (max) |     | 1   |      | mA    | $V_{il} = 0.0 V$                                                                   |

## **Reliability and Service Life**

| Characteristic            | Symbol | Min | Тур | Max | Units | Notes and Conditions |

|---------------------------|--------|-----|-----|-----|-------|----------------------|

| Mean time between failure | MTBF   | TBD |     |     | Hours | Telcordia SR-332     |

Other Specifications

| other specifications |                 |     |     |     |       |                      |

|----------------------|-----------------|-----|-----|-----|-------|----------------------|

| Characteristic       | Symbol          | Min | Тур | Max | Units | Notes and Conditions |

| Switching frequency  | F <sub>sw</sub> |     | 300 |     | kHz   | Fixed frequency      |

| Weight               |                 |     | 34  |     | g     |                      |

#### **Referenced ETSI standards:**

ETS 300 019: Environmental conditions and environmental tests for telecommunications equipment

ETS 300 019: Part 1-3 (1997) Classification of environmental conditions stationary use at weather protected locations ETS 300 019: Part 2-3 (1997) Specification of environmental tests stationary use at weather protected locations

#### EMC

**Electromagnetic Compatibility**

| Phenomenon | Port      | Standard    | Test level               | Criteria | Notes and conditions         |

|------------|-----------|-------------|--------------------------|----------|------------------------------|

| Immunity:  |           |             |                          |          |                              |

| ESD        | Enclosure | EN61000-4-2 | 6 kV contact<br>8 kV air |          | As per ETS 300 386-1 table 5 |

#### Performance criteria:

NP: Normal Performance: EUT shall withstand applied test and operate within relevant limits as specified without damage. RP: Reduced Performance: EUT shall withstand applied test. Reduced performance is permitted within specified limits, resumption to normal performance shall occur at the cessation of the test.

LFS: Loss of Function (self recovery): EUT shall withstand applied test without damage, temporary loss of function permitted during test. Unit will self recover to normal performance after test.

#### **Referenced ETSI standards:**

ETS 300 386-1 table 5 (1997): Public telecommunication network equipment, EMC requirements

ETS 300 132-2 (1996): Power supply interface at the input to telecommunication equipment: Part 2 operated by direct current (dc) ETR 283 (1997): Transient voltages at interface A on telecommunication direct current (dc) power distributions

| Material Ratings             |                      |

|------------------------------|----------------------|

| Characteristic - Signal Name | Notes and Conditions |

| Flammability rating          | UL94V-0              |

| Material type                | FR4 PCB              |

#### **Model Numbers** Model Input Output **Output Current** Typical Load Voltage Number Voltage (Max.) Efficiency Regulation 2.32-2.75 Vdc 25 A ±1.0% DDR12-25D08-AJ 10.8-13.2 Vdc 84% 1.16-1.375 Vdc 8 A See Tracking Spec.

**DC-DC Converters**

Input Characteristics

| Characteristic                      | Symbol                   | Min | Тур      | Max | Units              | Notes and Conditions                                                      |

|-------------------------------------|--------------------------|-----|----------|-----|--------------------|---------------------------------------------------------------------------|

| Input current - operating           | l <sub>in</sub>          |     | 7.2      |     | Adc                |                                                                           |

| Reflected ripple current            | <sup>I</sup> in (ripple) |     | 35<br>50 |     | mA rms<br>mA pk-pk | measured with external filter.<br>See Application Note 133 for<br>details |

| Input capacitance - internal filter | C <sub>input</sub>       |     | 420      |     | μF                 |                                                                           |

| Input capacitance - external filter | C <sub>bypass</sub>      |     | 10       |     | μF                 | Use large value ceramic                                                   |

# Electrical Charact. - V<sub>ddq</sub> O/P

| Characteristic                                    | Symbol                                     | Min   | Тур   | Max   | Units      | Notes and Conditions                                                                                                                                      |

|---------------------------------------------------|--------------------------------------------|-------|-------|-------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Nominal set-point voltage<br>Output voltage range | V <sub>ddq</sub> (nom)<br>V <sub>ddq</sub> | 2.316 | 2.316 | 2.750 | Vdc<br>Vdc | With no external trim resistor<br>For details on trimming the<br>output voltage see<br>Application Note 133                                               |

| Output set-point accuracy                         |                                            |       | ±1.5  | ±2.5  | %          | Using 1% trim resistors measured at minimum load                                                                                                          |

| Load regulation                                   |                                            |       | +0/-1 | +1/-2 | %          | Vary load with line held constant<br>(Voltage typically drops with load)                                                                                  |

| Line regulation                                   |                                            |       | ±0.1  | ±0.2  | %          | Vary line with load held constant                                                                                                                         |

| Cross regulation                                  |                                            |       | ±0.4  | ±0.6  |            | Vary load on $V_{tt}$ with load on                                                                                                                        |

|                                                   |                                            |       |       |       |            | V <sub>ddq</sub> held constant                                                                                                                            |

| Temperature co-efficient                          |                                            |       |       | 0.2   | mV/ºC      |                                                                                                                                                           |

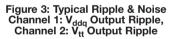

| Ripple and noise                                  |                                            |       |       | 50    | mV pk-pk   | With recommended external<br>load capacitance and<br>5 Hz to 20 MHz bandwidth                                                                             |

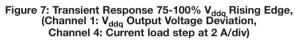

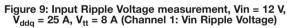

| Load transient response -<br>peak deviation       |                                            |       | 3     |       | %          | Peak deviation for 75% to 100%<br>step load, di/dt = 0.04 A/µs                                                                                            |

| Load transient response -<br>recovery             |                                            |       | 200   |       | μs         | Settling time to within 1% of<br>output setpoint voltage for<br>75% to 100% step load                                                                     |

| External load capacitance                         | C <sub>ext</sub> (V <sub>ddq</sub> )       | 1000  | 1680  | 3000  | μF         | Recommended 3 x 560 $\mu$ F with<br>total ESR of 5 m $\Omega$ and additional<br>high-quality ceramic capacitors.<br>Consult factory for other capacitance |

| Overshoot                                         |                                            |       |       | 2.0   | %          | Nominal output at turn-on                                                                                                                                 |

| Undershoot                                        |                                            |       |       | 150   | mVdc       |                                                                                                                                                           |

| Output current - continuous                       | l <sub>ddq</sub>                           | 1.5   |       | 25    | Adc        |                                                                                                                                                           |

| Output current - short circuit                    | lsc-ddq                                    |       | 0     |       | A rms      | Latching short circuit protection<br>power or enable needs to be<br>cycled                                                                                |

# Electrical Charact. - V<sub>tt</sub> O/P

| Characteristic                              | Symbol                              | Min  | Тур  | Max  | Units    | Notes and Conditions                                                                                                                             |

|---------------------------------------------|-------------------------------------|------|------|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Tracking accuracy                           |                                     |      | 12   | 25   | mV       | Measured at converter pins<br>(=V <sub>ddq</sub> /2 - V <sub>tt</sub> )                                                                          |

| Ripple and noise                            |                                     |      |      | 30   | mV pk-pk | With recommended external<br>load capacitance and<br>5 Hz to 20 MHz bandwidth                                                                    |

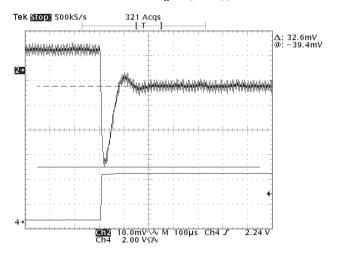

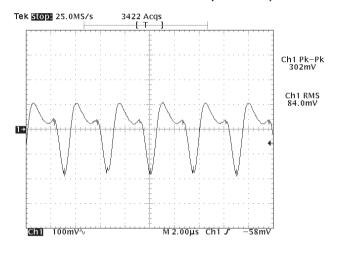

| Load transient response -<br>peak deviation |                                     |      | 3    |      | %        | Peak deviation for 75% to 100%<br>step load, di/dt = 8 A/µs                                                                                      |

| Load transient response -<br>recovery       |                                     |      | 200  |      | μs       | Settling time to within 1% of<br>output setpoint voltage for<br>75% to 100% step load                                                            |

| External load capacitance                   | C <sub>ext</sub> (V <sub>tt</sub> ) | 1000 | 1680 | 3000 | μF       | Recommended 3 x 560 $\mu$ F with total ESR of 5 m $\Omega$ and additional high-quality ceramic capacitors. Consult factory for other capacitance |

| Output current - continuous                 | Itt                                 | 0    |      | 8    | Adc      |                                                                                                                                                  |

| Output current - short circuit              | I <sub>sc-tt</sub>                  |      | 0    |      | A rms    | Latching short circuit protection<br>power or enable needs to be<br>cycled                                                                       |

| Protection and Control Features |                                     |     |          |     |            |                      |

|---------------------------------|-------------------------------------|-----|----------|-----|------------|----------------------|

| Characteristic                  | Symbol                              | Min | Тур      | Max | Units      | Notes and Conditions |

| Overcurrent limit inception     | l <sub>ddq</sub><br>I <sub>tt</sub> |     | 36<br>14 |     | Adc<br>Adc |                      |

| Efficiency     |        |     |     |     |       |                      |

|----------------|--------|-----|-----|-----|-------|----------------------|

| Characteristic | Symbol | Min | Тур | Max | Units | Notes and Conditions |

| Efficiency     | η      |     | 84  |     | %     | Full load            |

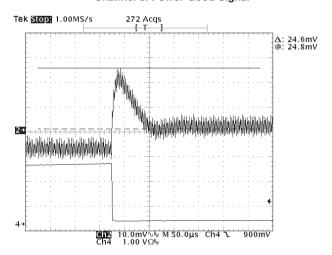

Figure 5: Transient Response 75-100%  $V_{tt}$  Source, Rising Edge (Channel 2:  $V_{tt}$  Output Voltage Deviation, Channel 4: Current load step at 1 A/div)

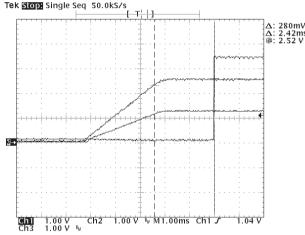

Figure 4: Typical Power-up Channel 1: V<sub>ddg</sub> Output Channel 2: V<sub>tt</sub> Output Channel 3: Power Good Signal

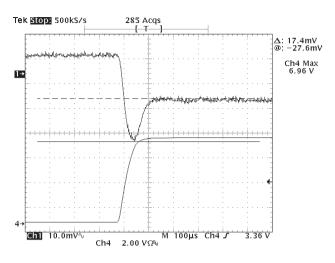

Figure 6: Transient Response 75-100%  $V_{tt}$  Source, Falling Edge (Channel 2:  $V_{tt}$  Output Voltage Deviation, Channel 4: Current load step at 1 A/div)

т

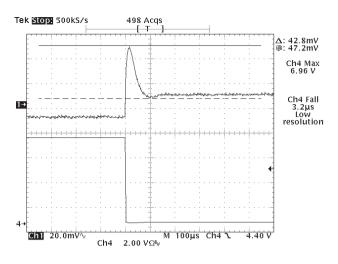

Figure 8: Transient Response 75-100% V<sub>ddq</sub> Falling Edge, (Channel 1: V<sub>ddq</sub> Output Voltage Deviation, Channel 4: Current load step at 2 A/div)

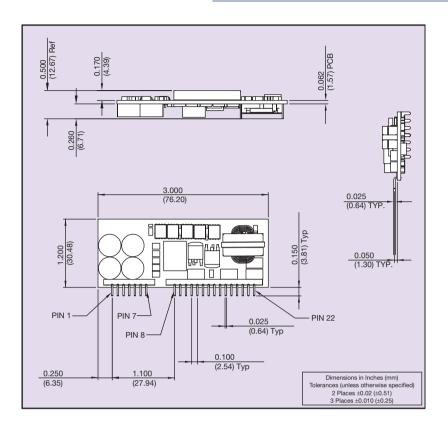

| Pin Connections |                      |         |                          |

|-----------------|----------------------|---------|--------------------------|

| Pin No.         | Function             | Pin No. | Function                 |

| J1-1            | Power Good           | J2-5    | Ground                   |

| J1-2            | Output Enable        | J2-6    | Ground                   |

| J1-3            | Ground               | J2-7    | Ground                   |

| J1-4            | Ground               | J2-8    | Ground                   |

| J1-5            | 12V Input            | J2-9    | V <sub>ddq</sub> Sense - |

| J1-6            | 12V Input            | J2-10   | V <sub>ddq</sub> Sense + |

| J1-7            | 12V Input            | J2-11   | V <sub>ddq</sub>         |

| J2-1            | V <sub>tt</sub> Ref. | J2-12   | V <sub>ddq</sub>         |

| J2-2            | V <sub>tt</sub>      | J2-13   | V <sub>ddq</sub>         |

| J2-3            | V <sub>tt</sub>      | J2-14   | V <sub>ddq</sub>         |

| J2-4            | Ground               | J2-15   | V <sub>ddq</sub>         |

Figure 10: Mechanical Drawing and Pinout Table

File Name: If\_ddr12.pdf Rev: 29 Nov 2005

### **DC-DC Converters**

#### Note 1

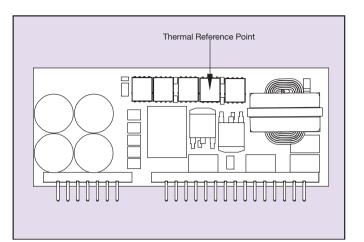

For maximum reliability temperature at the Thermal Reference Point, shown in Figure 11, should not exceed 100 °C.

#### Note 2

The control pin is referenced to Vin-

#### Note 3

The DDR12 is supplied as standard with active High logic. Control input pulled low: Unit Disabled Control input left open: Unit Enabled

### Note 4

Thermal reference set up: Unit mounted on an edge card test board 215 mm x 115 mm. Test board mounted vertically. For test details and recommended set-up see Application Note 133.

**CAUTION:** Hazardous internal voltages and high temperatures. Ensure that unit is accessible only to trained personnel. The user must provide the recommended fusing in order to comply with safety approvals.

**Figure 11: Thermal Reference Points**

e-mail: sales.us@artesvn.cor

☎ 800 769 7274

☎ + 508 628 5600

EUROPEAN LOCATIONS

e-mail: sales.europe@artesyn.com

**☎**+353 24 93130

AUSTRIA ☎+43 1 80150

FAR EAST LOCATIONS e-mail: sales asia@artesyn.com

HONG KONG \$\$\mathbf{\mathbf{m}}+852 2699 2868

Longform Datasheet © Artesyn Technologies® 2005

The information and specifications contained in this datasheet are believed to be correct at time of publication. However, Artesyn Technologies accepts no responsibility for consequences arising from printing errors or inaccuracies. Specifications are subject to change without notice. No rights under any patent accompany the sale of any such product(s) or information contained herein.